- 您现在的位置:买卖IC网 > Sheet目录251 > SGN08G72G1BB2SA-CCWRT (Swissbit NA Inc)SDRAM DDR3 8GB 204 SO-UDIMM

�� �

�

�

�Preliminary� Data� Sheet�

�Rev.0.9�

�20.09.2011�

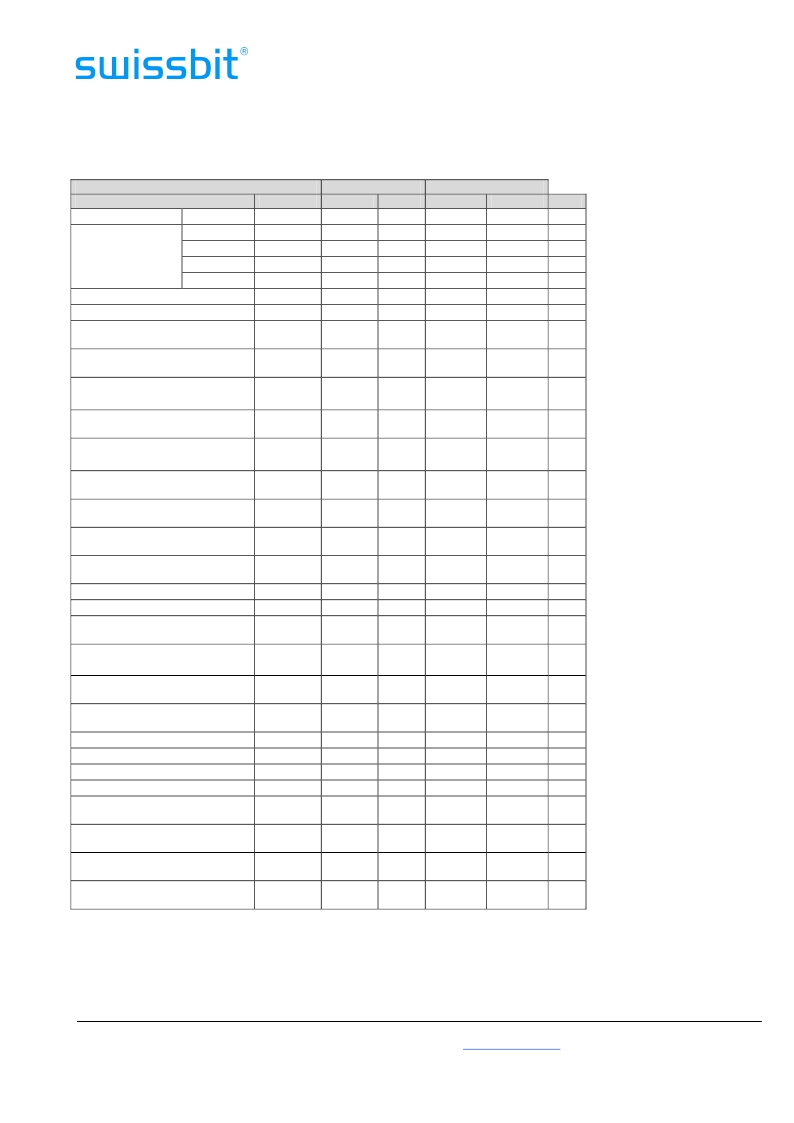

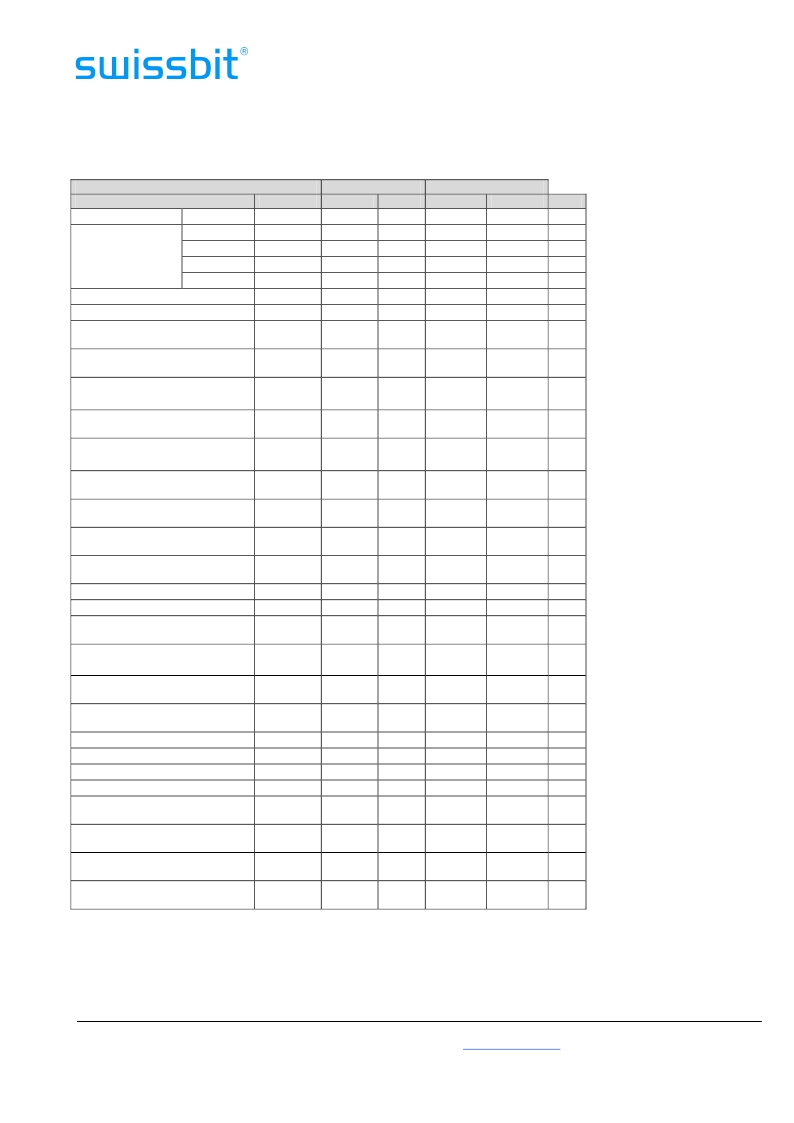

�DDR3� SDRAM� COMPONENT� ELECTRICAL� CHARACTERISTICS� AND� RECOMMENDED�

�AC� OPERATING� CONDITIONS�

�(0°C� ≤� T� CASE� ≤� +� 85°C;� V� DDQ� =� +1.5V� ±� 0.075V,� V� DD� =� +1.5V� ±� 0.075V)�

�AC� CHARACTERISTICS�

�10600-999�

�8500-777�

�PARAMETER�

�SYMBOL�

�MIN�

�MAX�

�Min�

�MAX�

�Unit�

�Clock� cycle� time�

�CL� =� 10�

�t� CK� (10)�

�1.5�

�<1.875�

�-�

�-�

�ns�

�CL� =� 9�

�CL� =� 8�

�CL� =� 7�

�CL� =� 6�

�CK� high-level� width�

�CK� low-level� width�

�Data-out� high-impedance�

�t� CK� (9)�

�t� CK� (8)�

�t� CK� (7)�

�t� CK� (6)�

�t� CH� (avg)�

�t� CL� (avg)�

�t� HZ�

�1.5�

�1.875�

�1.875�

�2.5�

�0.47�

�0.47�

�<1.875�

�<2.5�

�<2.5�

�3.3�

�0.53�

�0.53�

�250�

�-�

�-�

�1.875�

�2.5�

�0.47�

�0.47�

�-�

�-�

�<2.5�

�3.3�

�0.53�

�0.53�

�300�

�ns�

�ns�

�ns�

�ns�

�t� CK�

�t� CK�

�ps�

�window� from� CK/CK#�

�Data-out� low-impedance� window�

�t� LZ�

�-500�

�250�

�-600�

�300�

�ps�

�from� CK/CK#�

�DQ� and� DM� input� setup� time�

�t� DS(Base)�

�30�

�25�

�ps�

�relative� to� DQS�

�DQ� and� DM� input� hold� time�

�t� DH(Base)�

�65�

�100�

�ps�

�relative� to� DQS�

�DQ� and� DM� input� setup� time�

�t� DS1V�

�180�

�200�

�ps�

�relative� to� DQS� V� REF� =1V/ns�

�DQ� and� DM� input� hold� time�

�t� DH1V�

�165�

�200�

�ps�

�relative� to� DQS� V� REF� =1V/ns�

�DQ� and� DM� input� pulse� width�

�t� DIPW�

�400�

�490�

�ps�

�(� for� each� input� )�

�DQS,� DQS#� to� DQ� skew,� per�

�t� DQSQ�

�125�

�150�

�ps�

�access�

�DQ-DQS� hold,� DQS� to� first� DQ�

�t� QH�

�0.38�

�0.38�

�t� CK�

�to� go� non-valid,� per� access�

�(AVG)�

�DQS� input� high� pulse� width�

�DQS� input� low� pulse� width�

�DQS,� DQS#� rising� to/from� CK,�

�t� DQSH�

�t� DQSL�

�t� DQSCK�

�0.45�

�0.45�

�-255�

�0.55�

�0.55�

�255�

�0.45�

�0.45�

�-300�

�0.55�

�0.55�

�300�

�t� CK�

�t� CK�

�ps�

�CK#�

�DQS,� DQS#� rising� to/from� CK,�

�t� DQSCK�

�1�

�10�

�1�

�10�

�ns�

�CK#� when� DLL� disabled�

�DLL_DIS�

�DQS� falling� edge� to� CK� rising�

�t� DSS�

�0.2�

�0.2�

�t� CK�

�-� setup� time�

�DQS� falling� edge� from� CK� rising�

�t� DSH�

�0.2�

�0.2�

�t� CK�

�-� hold� time�

�DQS� read� preamble�

�DQS� read� postamble�

�DQS� write� preamble�

�DQS� write� postamble�

�Positive� DQS� latching� edge� to�

�t� RPRE�

�t� RPST�

�t� WPRE�

�t� WPST�

�t� DQSS�

�0.9�

�0.3�

�0.9�

�0.3�

�-� 0.25�

�Note1�

�Note2�

�+� 0.25�

�0.9�

�0.3�

�0.9�

�0.3�

�-� 0.25�

�Note1�

�Note2�

�+� 0.25�

�t� CK�

�t� CK�

�t� CK�

�t� CK�

�t� CK�

�associated� clock� edge�

�Address� and� control� input� pulse�

�t� IPW�

�620�

�780�

�ps�

�width� (� for� each� input� )�

�CTRL,� CMD,� Addr� setup� to� CK,�

�t� IS(Base)�

�65�

�125�

�ps�

�CK#�

�CTRL,� CMD,� Addr� setup� to� CK,�

�t� IS(1V)�

�240�

�300�

�ps�

�CK#�

�1�

�2�

�V� REF� @� 1V/ns�

�The� maximum� preamble� is� bound� by� t� LZDQS� (MAX)�

�The� maximum� postamble� is� bound� by� t� HZDQS� (MAX)�

�Swissbit� AG�

�Industriestrasse� 4�

�CH� –� 9552� Bronschhofen�

�Fon:� +41� (0)� 71� 913� 03� 03�

�Fax:� +41� (0)� 71� 913� 03� 15�

�www.swissbit.com�

�eMail:� info@swissbit.com�

�Page� 9�

�of� 15�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SGP1200-12G

FRONT END AC/DC 1133W 12V

SL05.TCT

TVS ARRAY DATA INTFC SOT-23

SL24T1G

TVS LO CAP 300W 24V ESD SOT23

SLD10U-022-B

DIODE TVS AXIAL HI-POWER

SLP-2-413-01

SNAP LOCK PINS TEAR-DROP .413"

SLVU2.8-4.TBT

IC TVS ARRAY 4-LINE 2.8V 8SOIC

SLVU2.8-8.TBT

IC TVS ARRAY 8-LINE 2.8V 8SOIC

SLVU2.8HTG

TVS DIODE ARRAY 1CH SOT23

相关代理商/技术参数

SGN08G72G1BB2SA-DCRT

制造商:SWISSBIT 功能描述:DDR3 SO-DIMM 8 GB 1600/CL11 - Trays 制造商:SWISSBIT NA INC 功能描述:DDR3 8GB SODIMM

SGN08G72G1BB2SA-DCWRT

功能描述:MODULE DDR3 SDRAM 8GB 204SOUDIMM 制造商:swissbit na inc. 系列:- 零件状态:过期 存储器类型:DDR3 SDRAM 存储容量:8GB 速度:1600MT/s 封装/外壳:204-SO-UDIMM 标准包装:100

SGN2M056TG

制造商:Panasonic Industrial Company 功能描述:DOOR

SGN72288FH8P6PH

制造商:SMART Modular Technology Inc 功能描述:MEMORY MODULE - Trays

SGN72568FH8P0PH

制造商:SMART Modular Technology Inc 功能描述:ECC 256MX8 .94" DDR3-1333 NVDIMM - Trays

SGN72568FH8YZPH

制造商:SMART Modular Technology Inc 功能描述:2GB 1.18" MINI-NVDIMM, 256MX8 - Trays

SGN-75

制造商:EGS ELECTRICAL GROUP 功能描述:GSK 4.625X1.562X0.125 NEO

SGNE010MK

制造商:SUMITOMO ELECTRIC Device Innovations Inc 功能描述:GaN HEMTs, MK16dB, 3.5GHz, 100mA, Bulk